在计算机视觉领域,神经网络在图像识别、图像分割和目标检测方面具有先进性能。然而,基于传统冯诺依曼架构的神经网络的分类和检测方法面临存算分离的计算难题。而忆阻器作为一种新型存算一体器件,由于非易失性和纳米尺寸等特性,非常适合实现神经突触。因此基于忆阻器的神经网络引起了广泛关注。

目前基于忆阻器的神经网络研究面临多态模型设计、循环神经网络(RNNs)中的核心模块门控循环单元(GRU)计算复杂等难题,我校微电子学院集成电路设计研究中心解光军教授、张章教授团队与上海交通大学微电子学院刘钢教授团队合作,针对性提出了相应解决方案,研究成果分别发表微电子领域国际著名期刊IEEE Transactions on Circuits and Systems II: Express Briefs和Transactions on Electron Devices。

在多态模型设计方面,门控忆阻器比传统的二端忆阻器具有明显的优势。目前由于难以实现大规模集成,开发一种灵活的门控忆阻仿真器对于探索神经网络的各种可能应用至关重要的。然而,现有的门控忆阻器模型缺乏灵活性和可移植性。团队进一步提出了一种门控忆阻器的新型FPGA模型,在Xilinx XQ7Z020芯片上进行了验证,硬件资源利用率低于1%。并提出了一种利用器件电导局部线性特性构建多重累积电路结构的新方法。此外,在MNIST数据集上验证了基于该模型的四态量化单层感知器。实验结果表明,该电路对10000张MNIST图像的识别精度达到87.6%,与PyTorch的结果仅相差0.03%。

该工作于2022年11月以“Gate-Controlled Memristor FPGA Model for Quantified Neural Network”为题发表在IEEE Transactions on Circuits and Systems II: Express Briefs。该研究得到了国家自然科学基金等经费支持。合肥工业大学为第一署名单位,我校张章教授为本文第一作者,程心老师为本文通讯作者。

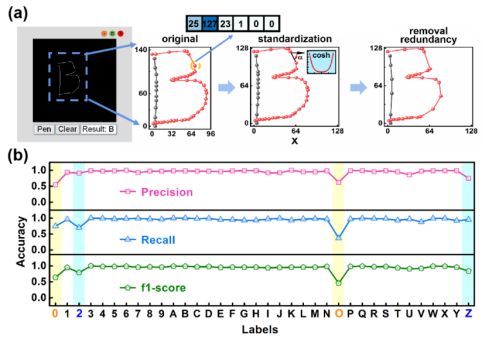

作为RNNs的核心模块门控循环单元(GRU)可将迭代乘法运算转化为累加运算,解决梯度爆炸或消失问题。然而,GRU模型的运算通常涉及大量的网络参数和迭代运算。使用传统的架构系统执行GRU模型需要大量的计算资源,而数据传输也限制了整体计算速度,在硬件实现上存在严重瓶颈。团队提出了一个基于忆阻器的GRU单元全电路。GRU电路作为循环神经网络工作的核心模块,具有充分的硬件实现和实际应用潜力。模拟实验显示电路模拟输出和软件模拟输出之间的平均误差相对较低,为1.07%,这说明该电路在GRU模型中显示出良好的兼容性。之后建立了一个八层GRU网络来处理手写字符序列检测任务,识别精度达到93%,预测任务精度达到92%。这表明所设计的GRU网络在处理时间序列数据时具有较好的性能。本工作扩展了基于忆阻器的神经形态计算系统在人工智能领域中的应用范围。

该工作于2022年12月在以“Memristor based Circuit Demonstration of Gated Recurrent Unit for Predictable Neural Network”为题发表在IEEE Transactions on Electron Devices。该研究得到了国家自然科学基金等经费支持。合肥工业大学为第一署名单位,我校张章教授为本文第一作者。